International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified Vol. 5, Issue 11, November 2016

# Implementation of Low Power and Area Efficient Shift Register by Register Reusing

S. Soundarya<sup>1</sup>, K. Prasanna<sup>2</sup>

PG Student, VLSI, Arasu Engineering College, Kumbakonam, India<sup>1</sup>

Assistant Professor, ECE, Arasu Engineering College, Kumbakonam, India<sup>2</sup>

Abstract: As the Word length of the shift register increases, the area and power consumption also increases. This paper proposes a low power and area efficient shift register by register reusing. In this system the multiple non-overlap delayed pulsed clock signals is used which timing problem between pulsed latches. The small number of pulsed clock signals used by grouping the latches to several subshift registers. Moreover, the similar functional operation of Register Reusing has been explained by using the Twisted Ring counter.

Keywords: Pulsed latches, pulsed Generator, Twisted Ring counter (TRC), Sub Shift Registers.

### I. INTRODUCTION

Since 1970's VLSI plays a major role in communication capacity. A computer or microprocessor-based system and semiconductor devices. VLSI (Very Large Scale commonly requires incoming data to be in parallel format. Integration) comprises thousands of transistors on a single But frequently, these systems must communicate with IC Chips. VLSI is majorly linked with Low power, Area and Speed. Mainly CPU, ROM and glue logic all these functions are performed on a single VLSI Chip. The dealy in the circuits The serial in -serial out shift register Power Consumption is important phenomenon in many applications. VLSI design builts its structures as such as design analysis, design implementation, computer-aided design, simution, testing. In VLSI modular technology it majorly deals with reducing interconnecting fabricating microchip Area. It is the one where rectangular blocks are constructed by repitive structures and they are connected by using wiring. For instance, the layout has been partioned into equal bit slices.

In digital circuits shift registers is used to construct many applications and it is the basic building block. It is constructed by connecting flipflops for data transmission and it is majorly used for shifting the data .flip-flops deals with the timing problem. So inorder to avoid timing problem we used Pulsed latches instead of flipflops. Thee A. SHIFT REGISTER: The Existing method comprises of pulsed latches also deal with timing problem but compared pulsed latches, flipflops produces larger timing problem. Shift registers are a type of sequential logic circuit, mainly for storage of digital data. They are a group of flip-flops connected in a chain so that the output from one flip-flop registers blocks and it also contains temporary storage becomes the input of the next flip-flop. Most of the latch to produce some time delay. registers possess no characteristic internal sequence of states. All flip-flop is driven by a common clock, and all are set or reset simultaneously

A register that allows each of the flip-flops to pass the stored information to its adjacent neighbour. The storage capacity of a register is the total number of bits (1 or 0) of digital data it can retain. Each stage (flip flop) in a shift register represents one bit of storage capacity. Therefore the number of stages in a register determines its storage

external devices that send or receive serial data. So, serialto-parallel conversion is required. Generally to produce can be used as a time delay device. The amount of delay can be controlled by: 1. the number of stages in the register 2. the clock frequency.

This paper proposes a N-bit shift Register by using register reusing concept. The pulsed latch has been used to reduce the time delay in the circuits. SSASPL (static sense differential amplifier shared Pulsed Latch) which is the smallest latch with less number of transistors. The same similar operation of latch and flipflop is explained by using twisted ring counter or simply called as Johnson counter.

#### **II. ARCHITECTURE**

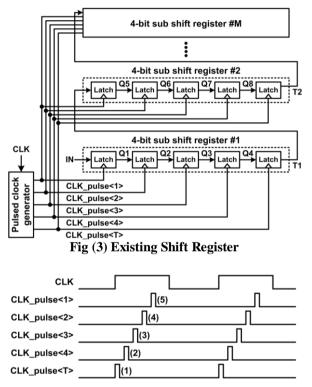

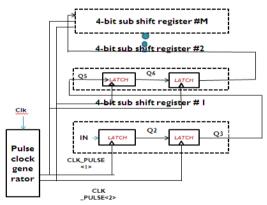

the design of the shift register by using pulsed latches. Moreover the Architecture of the shift register consists of pulsed clock generator which is used for generating clock pulses to the latches. Then, it also consists of sub-shift

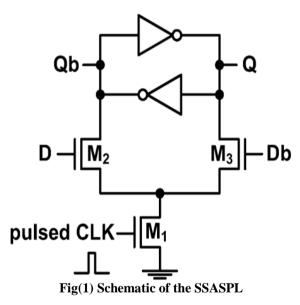

#### B. Ssaspl latch

As shown in the figure(1)static differential sense amp shared pulse latch).It consists of 7 transistors. The latch consists of one cross coupled inverters and it also consists of 3 NMOS transistors (M1-M3). The lowest clock power has been achieved because the pulsed clock signal is shared with one single transistor M1. The complementary data ouput has been obtained based on the data input D and Db. The three NMOS transistors has been designed as

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 11, November 2016

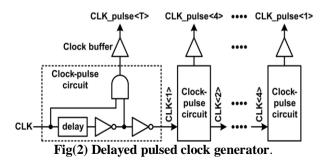

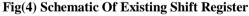

such transistors has been used to hold the data with four delayed pulsed clock signals are used to generating sharp transistors (cross-coupled-inverters). It also needs pulsed clock signals so that summation of rising and differential data inputs and pulsed clock signal. If the falling edge is shorter. The number of latches and clock pulsed clock signal input is high so it updates the data. The pulse circuits changes according to word length of the node q or qb is pulled down to ground according to the subshift registers. complementary data inputs. The output signals of the first latch (Q1 and Q1b) change correctly, because the input D.SUB-SHIFT REGISTERS signal of the first latch (IN) is constant during the clock pulse width . On the other hand, the output signals of the second latch (Q2 and Q2b) do not change, because the temporary storage latch named as T1-TM. It does not input signals of the second latch, which are connected to produce the same data to the next sub-shift registers it the output signals of the second latch (O2 and O2b), changes according to the input of the bit transferred to the change during the clock pulse width. The SSASPL flip the latches. Fig (3)show the block diagram of existing shift states of the cross-coupled inverters (Q and Qb) by pulling registers and fig(4)show the schematic waveform for current down through either or during the clock pulse existing shift register. width. The clock pulse width is selected as the minimum time to flip the output signals of the latch (Q and Qb) when its input signals (D and Db) are constant. If the input signals change during the clock pulse width, the time pulling current down through either or becomes shorter than the clock pulse width, so that the latch has not enough clock pulse time to flip the output signals after the input signals change.

#### C. DELAYED PULSE CLOCK GENERATOR

The pulsed clock generator consists of delay circuit AND gate. The delayed pulsed clock generator is useful for generating small pulsed clock signals. The AND gate and

The M number of stages of sub-shift registers has been used to shift the data through the latches (q1-q5).the

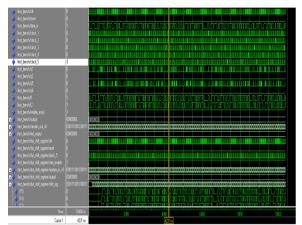

#### E. OUTPUT WAVEFORMS

Fig(5) Waveform of shift register

## IJARCCE

International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 11, November 2016

#### **III. PROPOSED ARCHITECTURE**

#### A. REGISTER REUSING

The Register Reusing is the concept introduced in the proposed shift register as shown in fig.7.The number of latches has been reduced .The structure consists of two The similar phenomenon of Register Reusing concept has latches .the shifting of data happens without delay. The structure consists of m-bit sub shift registers. The pulse generator which continuously provides clocks pulses to the latches. The operation of the existing shift register is same as performed by the proposed shift register. The same set of registers has reused to shift the data bits. Due to Register Reusing the area time and delay has been reduced greatly in proposed shift regiser.

Fig(7)proposed shift register

#### **B.OUTPUT WAVEFORMS**

Fig(8)waveform of Register Reusing

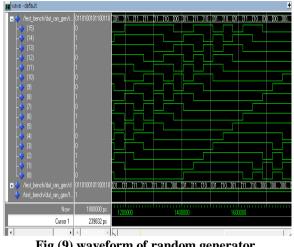

Fig (9) waveform of random generator

been explained in testing methodologies. The methodology has been explained by using twisted ring counter. If data volume increases simultaneously it need to change Automatic Test Equipment (ATE).and it requires Additional Test Application Time (TAT). To rectify the above problems we choose built in self test (BIST) and test data compression. The code based scheme compresses test data in the form of code words.

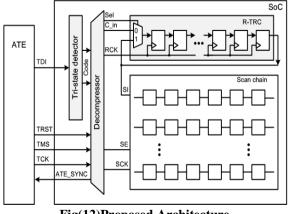

#### C. TWISTED RING COUNTER

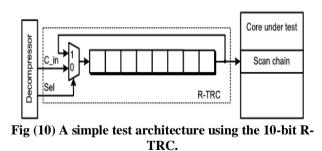

As shown in the fig (8) the Twisted Ring Counter (TRC) Consists of decompressor and multiplexer and scan chains. The TRC consists of flip-flops it is used to store the test data. The R-TRC block has been used to improving reuseable data. (i.e) the feedback and twist characteristics of R-TRC for reusing previously test data. The values used here are the tri-state values. The multiplexer needs feedback and twist mode. The Twistmode data can be selected based on C\_in data. The save and change of test data is based on the operation of multiplexer. The decompressor is used to continuously generate the data at a fixed length. scan chain receives the data signals. R-TRC is the general memory block to store the data inputs.

#### D. ARCHITECTURE

The method consists of Automatic Test Equipment (ATE), Tristate detector, Decompressor, R-TRC, scan chain.ATE is responsible for generating Test Data Inputs (TDI). The range information has been increased and ATE used does not require additional ports.

# IJARCCE

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 11, November 2016

responsible for decompressor and registers to analyse the where kk is [log2(llSSS+1)]. The CGU is responsible for as shown in the fig (10).

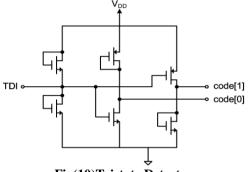

**Fig(10)**Tristate Detector

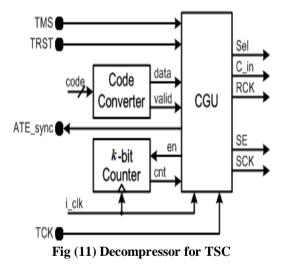

#### d. CONTROL AND GENERATOR UNIT

The code converter has simple combinational logic in order to identify the code data that are outputs of the tristate detector. It has two input and two output ports and its truth table is shown in Table VI.

Fig(12)Proposed Architecture

The tristate detector is that the TDI inputs has been is The kk-bit counter helps to control the CGU to enable the converted into 2-bit binary value .this conversion is shifting operation from the R-TRC to the scan chain, Hi-Z value. The tristate detector consists of only 6 controlling the R-TRC and the scan chain, delivering the transistors and it produces two ouputs in the form of codes decompressed test data to the scan chain, adjusting the suitable clocks among the ATE clock and the internal clock and synchronizing the clocks between the ATE and the internal circuit.

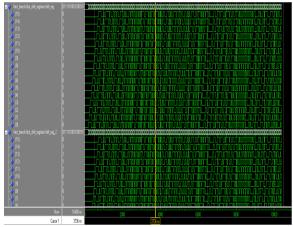

#### F. OUTPT WAVEFORMS

FIG (13) waveform of twisted ring counter

FIG (14) Waveform of Decompressor

#### **IV. CONCLUSION**

The proposed system uses the less number of latches compared to the existing system. The same shifting operation has been done in the Register Reusing concept. Moreover the Twisted Ring Counter explains the similar functional operation of Register Reusing in testing scenario. Thus area time, area and delay consumption has been reduced.

#### REFERENCES

[1] Anisha D and Mrs. Nirmala Devi. K," Pulsed Latch Based Low Power and Delay Effective Shift Register Using Trigger Generator", International journal of engineering science and technology, vol 3, issue 5, may 2016.

**IJARCCE**

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 11, November 2016

- [2] A. S. Abu-Issa," Energy-Efficient Scheme for Multiple Scan-Chains BIST Using Weight-Based Segmentation" IEEE trans, 2016.

- [3] Byung-Do Yang "Low power and Area –Efficient Shift register Using pulsed latches",IEEE Trans. On Circuit and systems vol.62,no.6,june 2015.

- [4] C. K. Teh, T. Fujita, H. Hara, and M. Hamada, "A 77% energysaving 22-transistor single-phase-clocking D-flip-flops with adaptive-coupling configurationin40nmCMOS," in IEEEInt.Solid-StateCircuitsConf. (ISSCC) Dig. Tech. Papers, Feb. 2011, pp. 338– 339

- [5] S. Heo, R. Krashinsky, and K. Asanovic, "Activity-sensitive flipflop and latch selection for reduced energy," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 9, pp. 1060–1064, uy89Sep. 2010.

- [6] ] Irith Pomeranz," Static test compaction for circuits with multiple independent scan chains", IET Comput. Digit. Tech., 2016, Vol. 10, Iss. 1.

- [7] Nikitha.N, Pramod Mutalik ," Front end Design of shift registers using latches ", International Research Journal of Engineering and Technology (IRJET), Volume: 03 Issue: 05, May-2016.

- [8] Sungyoul Seo, Yong Lee, and Sungho Kang, "Tri-State Coding using Reconfiguration of Twisted Ring Counter for Test Data Compression", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems ,2015.

- [9] H.-S. Kim, J.-H. Yang, S.-H. Park, S.-T. Ryan, and G.-H.Cho, "A 10-bitcolumn-driver IC with parasitic-insensitive iterative chargesharing based capacitor-string interpolation for mobile activematrix LCDs," IEEE J. Solid-State Circuits, vol. 49, no. 3, pp. 766– 782, Mar. 2014.

- [10] Syed Zaheer Ahamed, Imthiazunnisa Begum," Low-Power And Area-Efficient Shift Register Using Digital Pulsed Latches" International Journal & Magazine of Engineering, Technology, Management and Research, Volume No: 3 (2016), Issue No: 1 (January).

- [11] IP. Rahul Reddy," Analysis of Low-Power and Area-Efficient Shift Registers using Pulsed Latch", International Journal of Electronics and Communication Engineering (SSRG-IJECE) – Volume 3 Issue 1–January 2016

- [12] Mutum Arnica & Mr. Amit ," Low-Power and Area-Efficient Shift Register Using Pulsed Latch" Imperial Journal of Interdisciplinary Research (IJIR) Vol-2, Issue-8, 2016.

- [13] T.Shobakar, S.Muppudathi Sutha," An Optimized Shift Register Using Pulsed Latches" (IJRST) 2016, Vol. No. 6, Issue No. III, Jul-Sep 2016.

- [14] S. Zhang, C. Zhu, J. K. O. Sin, and P. K. T. Mok, "A novel ultrathin elevated channel low-temperature poly-Si TFT," IEEE Electron Device Lett., vol. 20, pp. 569–571, Nov. 1999.

- [15] M. Wegmuller, J. P. von der Weid, P. Oberson, and N. Gisin, "High resolution fiber distributed measurements with coherent OFDR," in Proc. ECOC'00, 2000, paper 11.3.4, p. 109.